What is the immediate limitation?

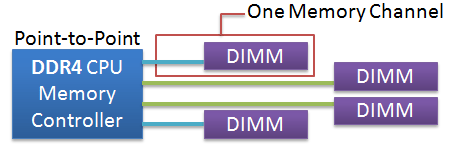

These lofty performance goals will go hand-in-hand with another change to the design: a single DIMM per channel. Yes, that means to get full performance, you will need a DIMM in every slot on the board.

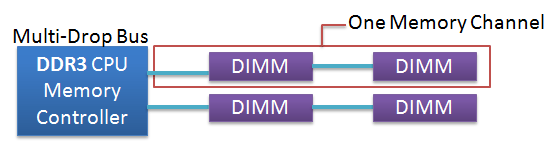

This follows on from the ongoing simplification of topology that has been a characteristic of the move from DDR to DDR2 and DDR3. You can find the details in our previous 'Secrets of PC memory' articles (Part 4 has the specifics) where the general rule of thumb was to remove as much difficulty in the timings as possible in order to scale clock speeds cheaply and efficiently using the same general DRAM technology and tooling.

This is the same process the PCI bus went through in its transition to PCI-Express: replacing anything parallel nature with a serial approach. DDR4 will become a point-to-point bus and the parallelism is being left with the memory controller itself with multiple memory channels.

If we look at Intel's upcoming LGA2011 socket that is anticipated to use a quad-channel memory interface and a single DIMM per channel, it's now quite obvious that future CPUs using this socket stand a good chance of using DDR4, especially as LGA1366 has had a well defined three year lifespan. In the same timeframe DDR4 could see considerable market acceptance so it's a smart move by Intel.

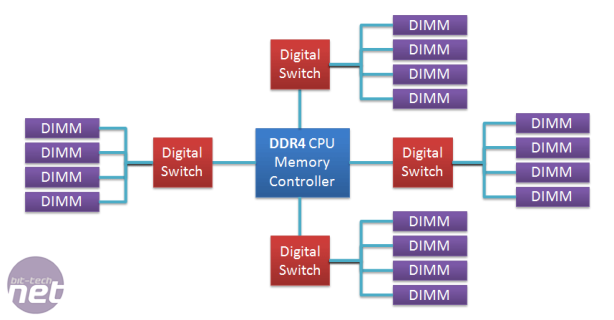

Server technology will be slightly different and use high performance digital switches to add additional DIMM slots per channel (much like PCI-Express switches we expect, but with some form of error prevention), and we expect it to be used with the latest buffered LR-DIMM technology as well, although the underlying DDR4 topology will remain the same.

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.